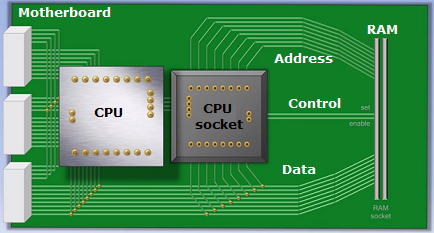

CPU är egentligen en komplex kretskort som innehåller flera processorer och komponenter som tillsammans utgör datorns processor, därför namnet Central Processing Unit. Processorer placeras på ett moderkort där alla trådar sammanbinder datorns hårdvara. Vi kan illustrera denna föreställning som följande:

Central Processing Unit (CPU) är faktiskt en komplex kretskortsenhet som omfattar flera processorer och komponenter som tillsammans utgör datorns huvudprocessor, därför namnet ”Central Processing Unit”. Processorer installeras på moderkortet där alla ledningar ansluter datorns hårdvara. Denna koncept kan illustreras på följande sätt:

De fina linjerna representerar trådarna som förenar datorkomponenterna; dessa trådar går under benämningen systembuss eller helt enkelt buss. I denna förenklade skiss visas hur processorn är sammankopplad med RAM-minnet och andra komponenter. Minnesstrukturen varierar, vilket leder till olika minnestyper, men huvudminnet, eller det primära minnet, är känt för att innehålla allt som processorn behöver för att utföra sina uppgifter. Detta innebär att det pågår ständig kommunikation mellan processorn och det primära minnet. Processorn kräver jo instruktioner för att behandla data, och dessa instruktioner återfinns i RAM-minnet. Se bilden nedan:

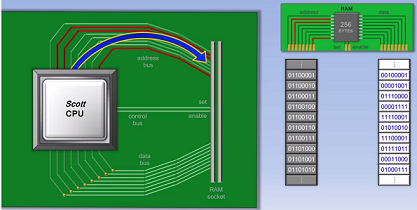

När en processor exekverar ett program, behöver den både instruktioner och data. Som sagt, dessa hämtas från RAM-minnet. Först måste processorn läsa av adresser som identifierar minnesceller där instruktioner och data lagras. När instruktionerna och datan har hämtats kan processorn exekvera instruktioner som load, add, store, compare, jump if, output, imput, och så vidare. Illustrationen nedan visar hur processorn använder sina egna register och RAM-minnet:

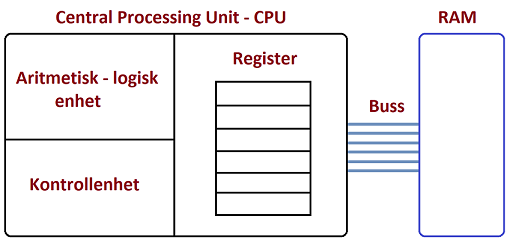

Enheten som tar emot instruktioner från minnet kallas för kontrollenhet och har som uppgift att hämta data och instruktioner, avkoda dem och samordna exekveringen av instruktioner genom en rad kommandon. Kontrollenheten samarbetar nära med en ALU-enhet (Arithmetic Logic Unit) som utför alla de beräkningar som processorn behöver under sitt arbete. Resultaten från kommandona lagras i olika register för vidare processhantering, och när processorn avslutar en arbetsuppgift lagras alla resultat på RAM-minnet. Se bilden nedan:

Att hämta samma instruktion eller data upprepade gånger från RAM-minnet till CPU tar tid. Denna tidsåtgång kan minskas om processorn är utrustad med ett snabbare minne kallat cacheminne. Cacheminnet är placerat inne i processorkretsen och det är där de instruktioner och data som används mest lagras. Cacheminnet finns i flera nivåer – L1, L2 och L3. Illustrationen nedan belyser en tvåkärnig processorarkitektur där varje kärna har sitt eget L1-cacheminne och processorn själv har ett L2-cacheminne.